Simulation-Driven Engineering Proof

Real post-layout SI, PI, and Thermal simulations executed using industry-grade solvers to validate high-speed, high-power designs.

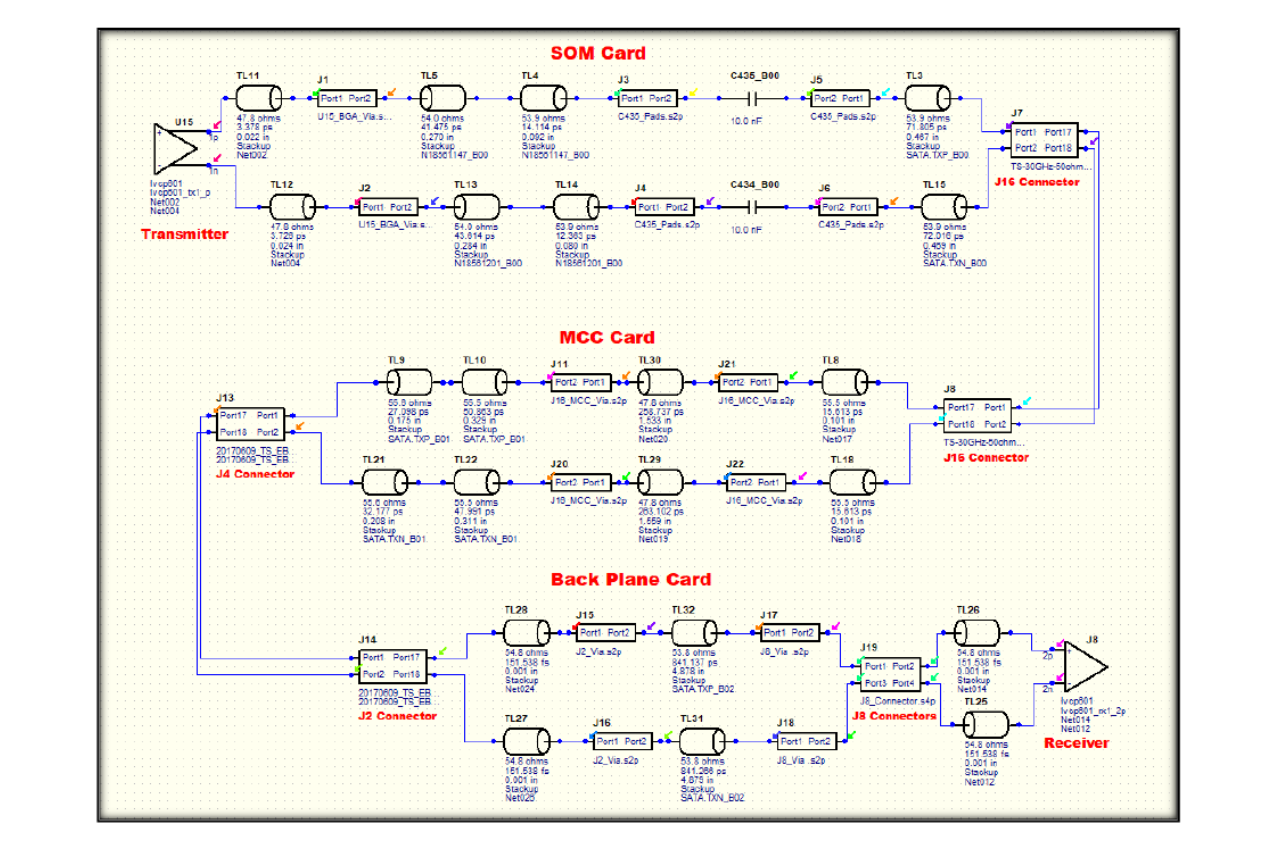

SGMII SERDES Signal Integrity

Post-layout eye diagram and channel analysis validating 1.25 Gbps SERDES compliance across SOM, MCC, and Backplane cards.

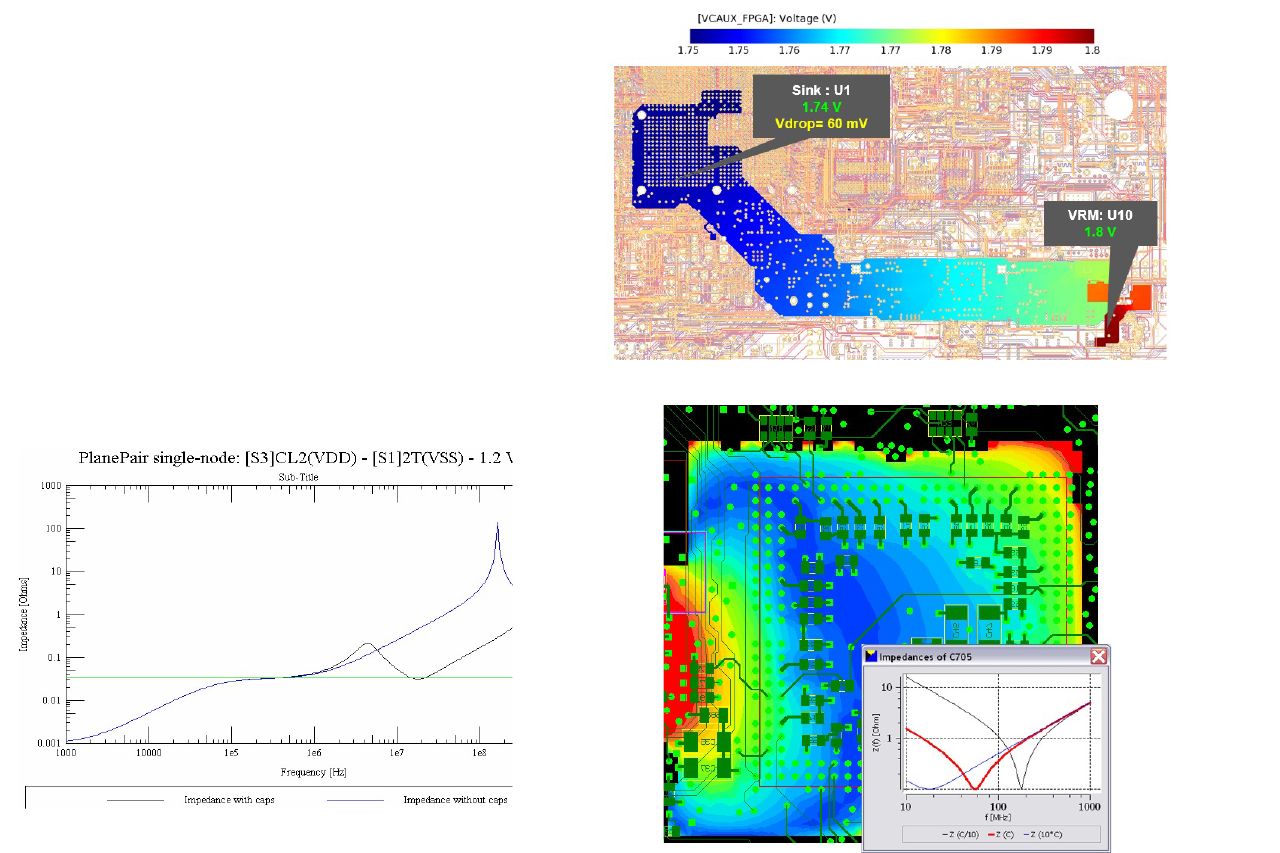

Power Integrity & PDN Analysis

Voltage drop, PDN impedance, and current density analysis ensuring stable power delivery under dynamic load conditions.

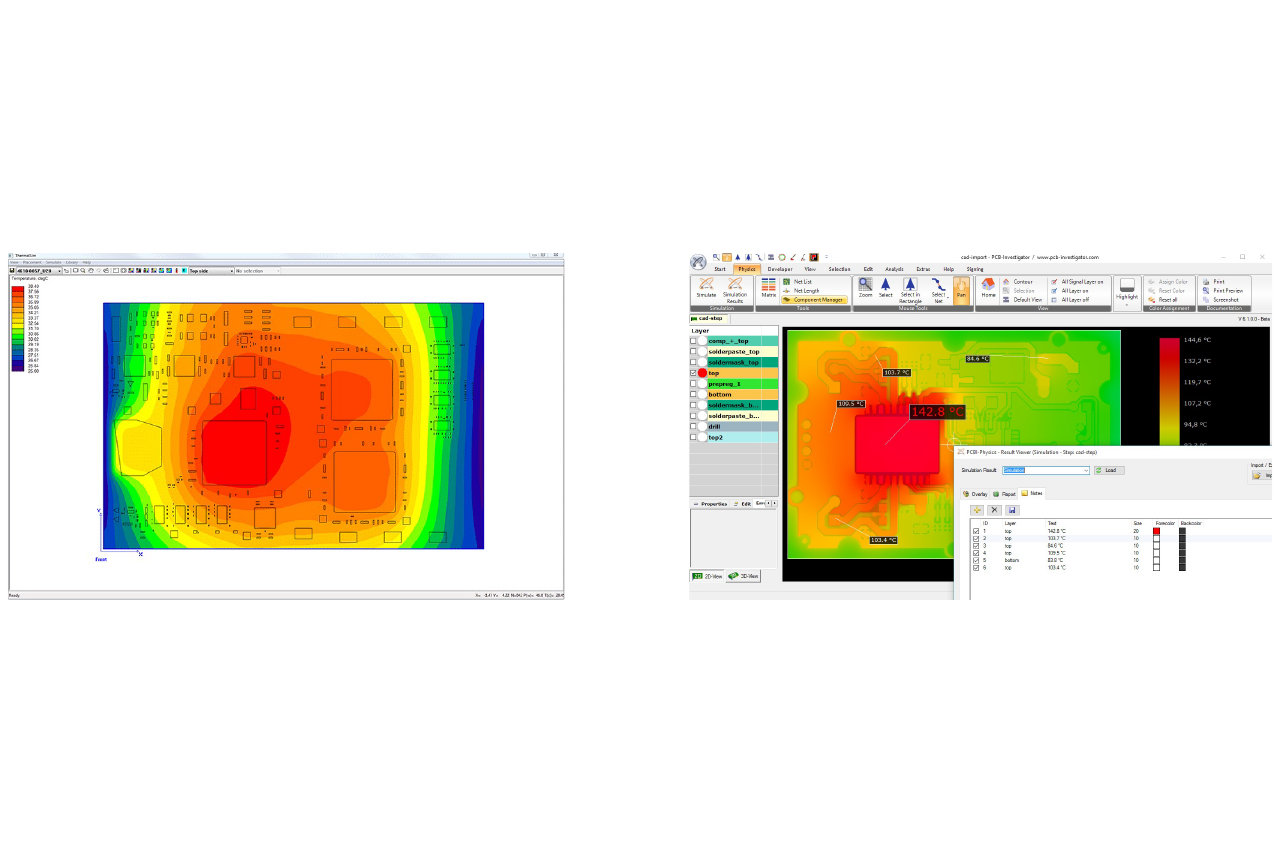

Thermal & Hot-Spot Analysis

Component-level thermal simulations identifying hot-spots and verifying junction temperatures under worst-case scenarios.